# Integrated Systems and Transformation of Microelectronics to Nanoelectronics

Prakrthi Bose\*

Department of Electronics and Communication, Mangalore University, Karnataka, India

#### Abstract

This paper is the study of transformational shift of microelectronics to nanoelectronics. Nanoelectronics are the electronic components manufactured on a nanoscale. The current electronics industry is far dependent on silicon based technologies which have reached their heights working at micro scale and defined Moore's law. Hence, there are existing technologies which can be approached further for micro miniaturizations. Nanomaterials are of very small size than micro and they exhibit rare self-assembling properties in them which are leading to the developments of integrated systems and their transformation from microelectronics to nanoelectronics.

Keywords: Micro-miniaturization, nano devices, MOSFET, simple conventional technique

\*Author for Correspondence: Email ID: drprakrthianbose.edu@gmail.com

#### **INTRODUCTION**

The various chip manufacturers have been relying upon this law for so long. Moore's law could not be continued forever in the electronics industry. Gordon Moore. predicted the number of transistors that could be placed on a chip, would double every two years <sup>[1]</sup>. By using this law they had achieved the exponential growth in transistor counts, but the scaling will end soon. The main obstacles are in the way: the limits of the lithography techniques, the rising cost of fabrication and the size of the transistor <sup>[2]</sup>. It was also observed that the contamination occurs during high temperature treatment of silicon <sup>[3]</sup>. Ultimately the goal of the scaling down process is to build an individual transistor which is smaller, faster, and cheaper and consumes less power. The use of the silicon in device manufacturing is going through the fundamental limitations including the tunneling current and the sub threshold current which lead to high power consumption and circuit failure <sup>[4]</sup>. Unfortunately, the scaling down of the

lithographically patterned transistors could not continue forever, but the nanoelectronics may be able to continue a small introduction to the metal oxide semiconductor field effect transistors.

#### **MOSFET BASICS**

Metal oxide semiconductor field effect transistor (MOSFET) is the major building block of the various computing devices. It is a four terminal device having the various terminals as drain, source, gate and the bulk <sup>[5]</sup>. In various digital circuits it is used as a switch. The source and the drain are the two ends of switch, while the channel is switched on and off under the control of gate voltage <sup>[5]</sup>. The MOSFET has been continuously scaled down to survive the Moore's law. Shrinking the feature size makes the transistor faster and consumes lesser power.

#### NANOELECTRONICS

After having known the physical and the fundamental limitations for the scaling down and the rising fabrication costs of MOSFET many researchers feel that the shift to the nanoelectronics would solve the problem. By mixing the fields of chemistry, biology, physics and the engineering; a solution to the rising fabrication cost and scaling down process may be achieved. The largest change in a shift to nanoelectronics is the method of fabrication. Individual wires, diodes, field effect transistors (FETs), and switches can be created abundantly and cheaply in a small setup. All of these devices would be so small that they may help reaching the smaller size integrated circuits (IC) which may not be possible with the conventional ICs. Nanoelectronics will be able to integrate the devices at a much smaller level and that too by overcoming all the problems that prevail in the case of conventional ICs.

## Technologies

The devices used to build a circuit are the fundamental elements for any circuit. For

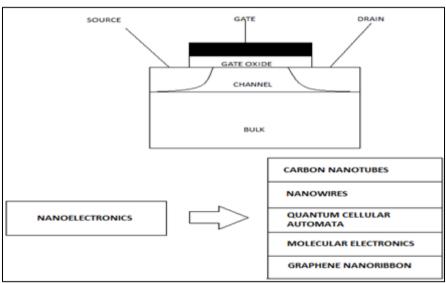

the present day very large scale integration (VLSI) systems; the silicon based transistors and copper wires are the fundamental elements. For nanoelectronics it appears that the silicon transistors and copper wires would be replaced by the nanoscale device technologies. The transformational move to nanoscale devices is because they can be chemically developed at much smaller sizes than the conventional elements which can be patterned with lithography. There are technologies innumerable which can replace the transistor in digital logic applications. They include carbon nanotube (CNT). semiconducting nanowire (S-NW), quantum cellular automata (QCA), molecular electronic devices and graphene nanoribbon (GNR). These devices offer sizes of a few nanometers and could be self-assembled. Figure 1 shows the schematic of various technologies that cover nanoelectronics.

Fig. 1: The Different Technologies for Nanoelectronics.

## Nanowires

These can be used as interconnect wires to carry the signals as well as active devices. Nanowires are long thin wires made up of the semi-conducting materials such as silicon or germanium that have been fabricated with a diameter less than 3 nm <sup>[6, 7]</sup> and a length of about few micrometers

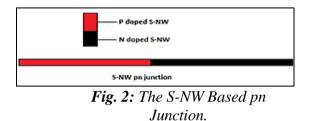

<sup>[8]</sup>. Using the semiconducting nanowire (S-NW) various devices can be manufactured. For making the transistor we can dope the silicon wire in such a way that it has a small centre section in which the number of carriers are less, that is, the low doping region is there <sup>[9]</sup>. After this; other S-NW is placed over the doped S-NW with an

insulator in between to make S-NW based FET <sup>[10]</sup>. To make the pn junction; we have to join the p-type S-NW with the n-type S-NW to create a contact <sup>[11]</sup>. Figure 2 shows the schematic of the S-NW based pn junction. The problems encountered by S-NW at the nano scale are like there is a tunneling of the current, the sub threshold current increases the power consumption and the leakage of the current <sup>[4]</sup>. These are some of the unavoidable problems of the S-NW at the nanoscale level occurs during high temperature treatment of silicon <sup>[3]</sup>.

At the first glance it seems that CNT and S-NW are similar to each other. But there are some differences which make the S-NW better technology than CNT. The main problem with the CNT is to grow the CNT at a large scale according to the desired properties. The present day methods to make a metallic and the semiconducting CNT vary according to the tube. However, in case of the S-NW these parameters could be easily controlled. The doping level can also be controlled in case of the S-NW whereas the CNT would either be metallic or semiconducting in nature.

## Quantum Cellular Automata

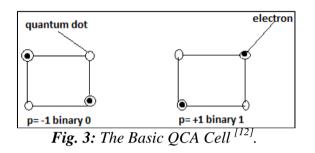

It is a computational model made up of quantum dots. Basically a quantum dot encodes the information by looking upon the position of the electron <sup>[12]</sup>. It traps the electron by establishing a low potential region surrounded by high potential region. The nanometer quantum dots are constructed by using the aluminum by nano imprint lithography techniques <sup>[13]</sup>. The logic unit in quantum cellular

automata (QCA) is the QCA cell proposed by the researchers at the University of Notre Dame. The QCA cell is composed of 4 or 5 quantum dots (Figure 3) <sup>[12]</sup>. A quantum dot is a nanometer sized structure capable of trapping the electron. They are created by an island of conductive material surrounded by insulating material. Electrons which will enter the quantum dots will get confined over there because of the high potential required to escape. Figure 3 shows the basic QCA cell.

In Figure 3 a basic logic decision for 1 and 0 has been shown by using the QCA cell structure. It gives the basic decision of the 1 and 0 by making use of the relative position of the electrons inside the quantum well <sup>[12]</sup>. So this basic QCA cell can be used to realize various logically operating devices and can replace the conventional microelectronics.

## **Molecular Devices**

Even though CNT, S-NW and QCA cell can be used as active devices as well as wires in Nano electronics, there is also a set of molecules that could be used as the active devices. These molecules behave as diodes or programmable switches that can make up the programmable connections between wires. Chemists have designed these carbon-based molecules to have electrical properties similar to their solidstate counterparts. Molecular devices have one huge advantage over solid-state devices i.e. their size. Thousands of molecules can be sandwiched between micro-scale wires to create an active device that takes up very little area. Since molecular devices fit between the wires, large area could be saved. It has been estimated that the use of S-NW and molecular switches could reduce the area of a field programmable gate array (FPGA) by 70% over a traditional SRAM based design at a 22 nm process <sup>[14]</sup>. In addition to being very small, molecular electronic based devices are nonvolatile. The configuration of the molecules remains stable in the absence of electric field.

## **Graphene Nanoribbon**

In this process of scaling down the scientists found a new material named graphene which had very good properties and had shown a ray of hope to be used as a replacement material for the silicon. So, since then graphene has been regularly discussed and has been investigated extensively to help produce a new generation of the electronics. Basically graphene is a material made up of carbon atoms arranged in 2d honevcomb lattice and can be utilized to make the various other carbon based materials, namely Bucky-ball carbon structure, carbon nanotubes, graphene nano-ribbons and the graphite<sup>[15]</sup>.

Hence it makes the ballistic transport possible even at the scaled down device compared to the CMOS technology at present. An added advantage in graphene is that the electronic transport follows the Dirac equation and the charge carriers are relativistic in nature <sup>[16]</sup>. Also the carriers have shown to be having zero effective mass and travel at the speed of light which makes the use of graphene into the devices more favorable as they will work at higher speed <sup>[16]</sup>.

However the use of the graphene in the digital based applications was not made because that it lacked the energy band gap. Thus, in spite of having high carrier mobility and significant current characteristics the graphene could not be

used in digital applications because the conduction in graphene could not be switched off due to the absence of band gap. In the meantime some research workers were able to propose a bilayer graphene complementary field effect transistor <sup>[17]</sup>.

This showed high on/off ratio making an important step towards graphene based logic devices <sup>[17]</sup>. One of the ways to open the band gap is patterning the graphene sheets into narrow ribbon <sup>[18]</sup>. Scanning tunneling microscope (STM) lithography is the process by which an energy gap can be introduced in a precise manner, turning the metallic graphene into semiconductor <sup>[18]</sup>.

The energy band gap is inversely dependent on the width of the graphene nanoribbon <sup>[19–25]</sup>. So by tuning the width of the graphene nanoribbon we can get the desired energy band gap. By cutting the graphene sheet into different length and width we can create the graphene nanoribbon (GNR). This nanoribbon can further be utilized to replace interconnects because of their high carrier mobility's and other exceptional properties <sup>[26–34]</sup>. Also we can use the GNR of different types to form a graphene field effect transistor (GFET).

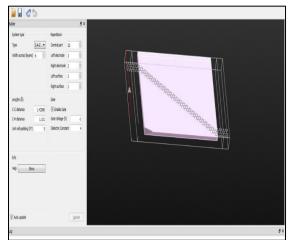

The proposed graphene nanoribbon (GNR) device has the electrodes part made up of zigzag graphene structure, that is metallic in nature and the central portion, which acts as a channel or conducting portion, is made up of semiconducting arm-chair shaped graphene.

The 3-terminal device as shown below (Figure 4) could be formed which is gate enabled and hence can work as a replacement for the present day transistor. Figure 4 shows the schematic diagram of the G-FET device.

Fig. 4: The G-FET Device.

#### **CONCLUSION**

The future electronic circuits are getting smaller but there is no compromise with their performance. The CNTs, S-NW, OCA, molecular electronic devices and graphene nanoribbon could easily replace the conventional microelectronics and lead to the miniaturization of the integrated circuits (IC). This will be huge leap in technology which will use small size electronic components and lead to increase in the density. The need of hour is to model robust methods for fabrication processes that can be used to process these advanced technology devices at a larger scale. Attaining control over the interfaces of these devices would further help in creating nanoscale integrated circuits. This achievement would pave a path towards interfacing nanoscale electronic devices with ultra-dense integrated circuitry. Table 1 gives the summary of different nanoelectronics techniques.

| <b>Table 1:</b> Summary of Different Nanoelectronics Techniques. |        |                     |              |                                       |

|------------------------------------------------------------------|--------|---------------------|--------------|---------------------------------------|

| Technology                                                       | Size   | Fabrication         | Lithography  | Problems                              |

| CNT                                                              | Few nm | Complex             | STM          | Fabrication problem                   |

| S-NW                                                             | Few nm | Simple conventional | Conventional | Tunneling of current and subthreshold |

|                                                                  |        | technique           | technique    | current                               |

| QCA                                                              | Nm     | Simple              | Nano imprint | Applicable in logic devices only      |

| Molecular                                                        | Nm     | Complex             | STM          | Practical implementation              |

| Device                                                           |        |                     |              |                                       |

| GNR                                                              | Few nm | Complex             | STM          | No problem                            |

## REFERENCES

- Law. 1. Moore's Encyclopedia Britannica, Encyclopædia Britannica Online, Encyclopedia Britannica Inc. 2013. Web, 14 May 2013.

- Lloyd 2. Harriott R. Limits of Lithography. Proceedings of the IEEE. Mar 2001; 89(3): 366–374p.

- 3. Schmidt PF, Pearce CW. A Neutron Activation Analysis Study of the Sources of Transition Group Metal Contamination in the Silicon Device Manufacturing Process. J Electrochem Soc. Mar 1981; 128(3): 630–637p.

- 4. Frank DJ, Dennard RH, Nowak E, et al. Device Scaling Limits of Si MOSFETs and Their Application Dependencies. Proceedings of the IEEE. 2001; 89(3): 259-288p.

- 5. Jaeger RC. Microelectronic Circuit Design. Boston, MA, WCB/McGraw-Hill. 1997.

- 6. Cui Y. Diameter-Controlled Synthesis of Single-Crystal Silicon Nanowires. Appl Phys Lett. 2001; 78(15): 2214-2216p.

- 7. Morales AM, Lieber CM. A Laser Ablation Method for the Synthesis of Crystalline Semiconductor Nanowires. Science. 1998; 279(5348): 208-211p.

- 8. Wu Y, Yang P. Germanium Nanowire Growth via Simple Vapor Transport. Chem Mater. 2000; 12: 605-607p.

- 9. Gudiksen M. Growth of Nanowire Superlattice Structures for Nanoscale Photonics and Electronics. Letters to Nature. 2002; 415(6872): 617-620p.

- 10. HuangY. Logic Gates and Computation from Assembled Nanowire Building Blocks. *Science*. 2001; 294(5545): 1313–1316p.

- Cui Y, Lieber CM. Functional Nanoscale Electronic Devices Assembled Using Silicon Nanowire Building Blocks. Science. 2001; 291(5505): 851–853p.

- Lent CS, Tougaw PD. Lines of Interacting Quantum-Dot Cells: A Binary Wire. J Appl Phys. 1993; 74: 6227–6233p.

- Hirai Yoshihiko, Yoshida Satoshi, Okuno H, et al. Aluminum Quantum Dots Fabrication by Nano-Imprint Lithography. *Microprocesses and Nanotechnology Conference 2000 International*. Jul 2000; 292–293p.

- 14. Gayasen A, Vijaykrishnan N, Irwin MJ. Exploring Technology Alternatives for Nano-Scale FPGA Interconnects. 42nd Proc. Design Automation Conference (DAC05). 2005; 921–926p.

- Geim AK, Novoselov S. The Rise of Graphene. J Nat Mater. 2007; 6: 183– 191p.

- Novoselov KS, Geim AK, Morozov SV, et al. Two Dimensional Gas of Mass Less Dirac Fermions in Graphene. J Nature. 2005; 438: 197– 201p.

- 17. Majumdar K, Murali KVRM, Bhat N, et al. High on-Off Ratio Bi layer Graphene Complementary Field Effect Transistors. Electron Devices Meeting (IEDM) 2010 IEEE International. Dec 2010.

- Levente Tapaszto, Gergely Dobrik, Philippe Lambin, *et al.* Tailoring the Atomic Structure of Graphene Nano Ribbons by Scanning Tunneling Microscope Lithography. *Nat Nanotechnol.* Jun 2008; 3: 397–401p.

- 19. Han Melinda Y, Barbaros Ozyilmaz, Yuanbo Zhang, *et al.* Energy Band-Gap Engineering of Graphene Nanoribbons. *J Phys Rev Lett.* May 2007; 98.

- 20. Behzad Razavi. *Design of Analog CMOS Integrated Circuits*. Tata McGraw Hill Edition. 2002. 21st Reprint 2011.

- Bin Yu, Haihong Wang, Riccobene C, et al. Limits of Gate-Oxide Scaling in Nano-Transistors. VLSI Technology, 2000, Digest of Technical Papers, 2000 Symposium. Jun 2000; 90(91): 13–15p.

- 22. Zhou C, Kumar A, Ryu K. Small Wonder: The Exciting World of Carbon Nanotubes. *IEEE Nanotechnol Mag.* 2007; 1(1): 13–17p.

- Baughman RH, Zakhidov AA, de Heer WA. Carbon Nanotubes-The Route toward Applications. *Science*. 2002; 297(5582): 787–792p.

- 24. McEuen PJ. Single-Wall Carbon Nanotubes. *Phys World*. 2000; 13(6): 31–36p.

- Iijima S. Helical Microtubules of Graphitic Carbon. *Nature*. 1991; 354(6341): 56–58p.

- 26. Raja T, Agrawal VD, Bushnell ML. A Tutorial on the Emerging Nanotechnology Devices. *Proc. 17th International Conference. VLSI Design.* 2004; 343–360p.

- Graham AP. How Do Carbon Nanotubes Fit into the Semiconductor Roadmap? *Appl Phys A Mater Sci Process.* 2005; 80(6): 1141–1155p.

- 28. Bachtold A. Logic Circuits with Carbon Nanotube Transistors. *Science*. 2001; 294: 1317–1320p.

- 29. Martel R. Single and Mulitwall Carbon Nanotube Field-Effect Transistors. *Appl Phys Lett.* 1998; 73(17): 2447– 2449p.

- Krupke R. Seraration of Metallic from Semiconducting Single-Walled Carbon Nanotubes. *Science*. 2003; 301(5631): 344–347p.

- Butts M, DeHon A, Goldstein SC. Molecular Electronics: Devices, Systems and Tools for Gigagate, Gigabit Chips. *IEEE/ACM Int'l Conf. Computer Aided Design (ICCAD02)*. 2002; 430–440p.

- 32. Novoselov KS, Geim AK, Morozov SV, *et al.* Electric Field Effect in Atomically Thin Carbon Films. *J Science*. Oct 2004; 306: 666–669p.

- 33. Berger C, Song Z, Li X, *et al.* Electronic Confinement and Coherence in Patterned Epitaxial Graphene. *J Science*. Apr 2006; 312: 1191–1196p.

- 34. Banerjee S, Sardar M, Gayathri N, *et al.* Enhanced Conductivity in Graphene Layers and at their Edges. *J Appl Phys Lett.* 2006; 88: 06211–1–06211–3p.